Ассоциация JEDEC, устанавливающая отраслевые нормы для типов памяти, находится на финальной стадии создания SPHBM4 (Standard Package High Bandwidth Memory) — свежего стандарта, призванного обеспечить полную пропускную способность уровня HBM4 через «суженный» 512-битный интерфейс. Он предлагает увеличенный объём памяти и снижает стоимость внедрения благодаря совместимости с обычными печатными платами. В случае массового принятия эта технология сможет занять множество рыночных ниш, потенциально доступных для HBM.

Источник изображения: Micron

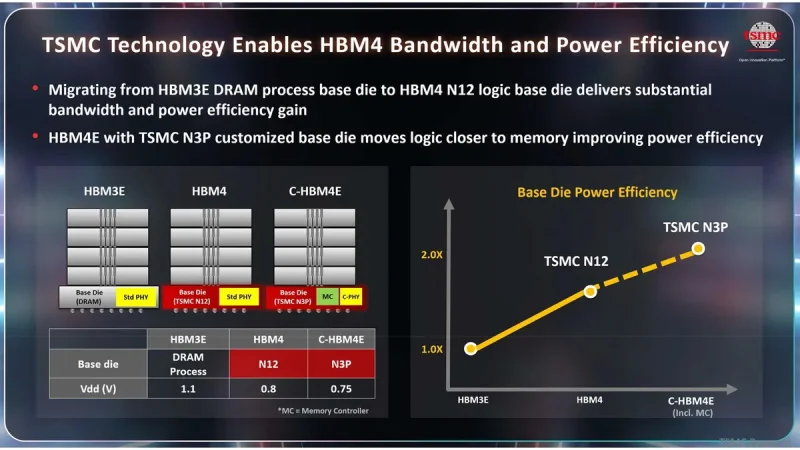

Несмотря на то, что чипы HBM с 1024-битным или 2048-битным интерфейсом демонстрируют выдающуюся производительность и энергоэффективность, их интеграция требует значительной площади на кристалле высокопроизводительных процессоров. Это ограничивает количество устанавливаемых модулей HBM и, как следствие, доступный объём памяти для ИИ-ускорителей, что сказывается на их индивидуальной мощности и потенциале крупных вычислительных кластеров.

Конструкция стандартного корпуса SPHBM4 решает эту задачу, сокращая ширину шины с 2048 до 512 бит и применяя сериализацию 4:1 для сохранения исходной пропускной способности. JEDEC не раскрывает деталей, подразумевает ли «сериализация 4:1» увеличение скорости передачи данных до 8 ГТ/с, как в HBM4, или же иную схему кодирования на повышенных частотах. Однако цель ясна: добиться аналогичной HBM4 совокупной пропускной способности, но при использовании 512-битного интерфейса.

Внутри корпусов SPHBM4 будет применяться стандартное HBM4-ядро, что упростит проектирование контроллера (по крайней мере, на логическом уровне) и позволит сохранить ёмкость на модуль на уровне HBM4 и HBM4E (до 64 ГБ для HBM4E), преобразовав интерфейс в более узкую шину. Теоретически это открывает возможность увеличить объём памяти SPHBM4 в четыре раза по сравнению с HBM4. На практике же разработчики ИИ-чипов, вероятно, будут искать компромисс между объёмом памяти и вычислительной мощностью, поскольку стоимость площади кристалла продолжает расти с каждым новым технологическим процессом.

Почему бы не рассмотреть применение памяти SPHBM4 в игровых видеокартах? Это могло бы обеспечить им существенно более высокую пропускную способность при умеренном росте стоимости в сравнении с решениями на базе GDDR7 или потенциальной GDDR7X с кодированием PAM4.

Созданная для достижения пропускной способности, соответствующей уровню HBM4, память SPHBM4 изначально проектировалась с акцентом на быстродействие и объём, в ущерб таким факторам, как энергоэффективность и цена. Несмотря на то, что SPHBM4 дешевле, чем HBM4 или HBM4E, её производство по-прежнему предполагает многослойную компоновку кристаллов, которые имеют большие физические размеры и, как следствие, более высокую стоимость по сравнению с обычными чипами DRAM. Это включает в себя базовый кристалл интерфейса, обработку сквозных кремниевых переходов (TSV), использование проверенных производственных процессов и сложную упаковку. Данные этапы формируют основную часть затрат и плохо поддаются масштабированию при росте объёмов выпуска, в отличие от стандартной GDDR7, которая выигрывает от огромных масштабов потребительского и игрового рынков, простых корпусов и отработанной технологии монтажа на плату. Замена нескольких чипов GDDR7 одним усовершенствованным модулем SPHBM4 может не привести к снижению издержек, а, напротив, увеличить их.

Несмотря на то, что 512-битная шина памяти остаётся сложным интерфейсом, по заявлению JEDEC, SPHBM4 позволяет осуществлять 2.5D-интеграцию на обычных текстолитовых подложках, не требуя дорогостоящих межсоединений. Это существенно сокращает затраты на интеграцию и потенциально расширяет возможности при проектировании. В то же время, благодаря стандартизированному 512-битному интерфейсу, SPHBM4 может предложить более низкую стоимость (за счёт эффекта масштаба, достигаемого стандартизацией) в сравнении с решениями C-HBM4E, которые используют интерфейсы UCIe или собственные проприетарные разработки.

В сравнении с решениями на кремниевой основе, разводка на текстолитовой подложке допускает использование более протяжённых электрических трасс между системой на кристалле (SoC) и стеками памяти. Это потенциально снижает ограничения по компоновке в крупногабаритных корпусах и позволяет разместить больший объём памяти вблизи процессорного узла, чем это возможно сегодня.