Ericsson анонсировала свою первую линейку продуктов AI-RAN, подтверждая курс на использование собственных ASIC для увеличения эффективности сетей радиодоступа (RAN). В то время как отрасль беспроводной связи всё активнее переходит на виртуализированные и облачные RAN-решения, построенные на универсальных процессорах (GPP) Intel, Ericsson продолжает вкладываться в специализированные чипы для ресурсоёмких операций, как отмечает IEEE ComSoc Technology Blog. При этом Intel остаётся для Ericsson стратегическим партнёром, тогда как сотрудничество с AMD и NVIDIA не сложилось.

Портфель Ericsson для сетей RAN строится на двух ключевых архитектурных подходах. Основная часть решений использует ASIC, созданные как самой компанией, так и совместно с Intel. Кроме того, в него входит Cloud RAN, где программная платформа Ericsson работает на процессорах Intel Xeon EE. Несмотря на ожидания рынка, что виртуализация позволит полностью отделить программное обеспечение от аппаратной части, Intel на сегодня — единственный поставщик микросхем для Ericsson в рамках масштабных внедрений, что несёт в себе определённые риски.

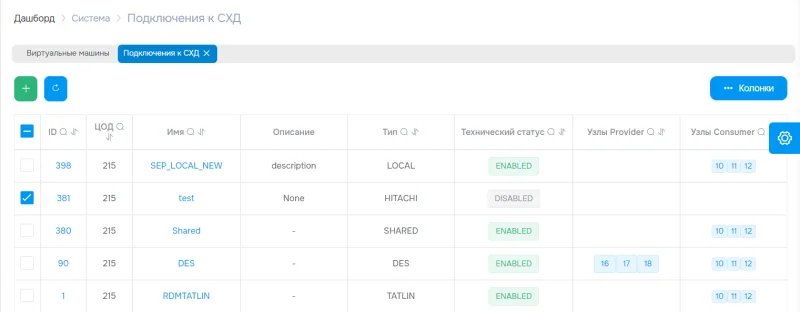

Источник изображений: Ericsson

Фактически Ericsson предоставляет «коммерческую поддержку» только для решений на базе Intel, в то время как для платформ AMD, Arm и NVIDIA всё ограничивается стадией «поддержки прототипов». Хотя в отрасли уже много лет говорят о важности разнообразия чипов в экосистеме vRAN, реальный прогресс в этом направлении, судя по всему, замедлился. Более того, внедрение искусственного интеллекта в программное обеспечение RAN добавляет новые сложности, которые могут усилить зависимость компании от аппаратных решений единственного поставщика.

Эксперты отрасли сохраняют скептицизм относительно амбиций Ericsson по созданию «единого программного стека» для разнородного оборудования. Хотя разделение аппаратной и программной частей достижимо на верхних уровнях сети (L2/L3), физический уровень L1 — наиболее требовательный к ресурсам — по-прежнему глубоко оптимизируется под конкретные чипы. Изначально Ericsson надеялась обеспечить переносимость кода L1 между архитектурами x86 (включая AMD) и Arm SVE2 (NVIDIA Grace), чтобы соответствовать производительности Intel AVX-512. Однако достижение высокой эффективности на этих платформах без масштабной переработки кода остаётся сложной инженерной задачей.

Ключевым узким местом в обработке трафика на уровне L1 является коррекция ошибок (FEC), которая традиционно требует специализированного аппаратного ускорения. Изначально Ericsson использовала подход с разгрузкой вычислений, передавая задачи FEC на дискретные ускорители Intel через интерфейс PCIe. Позже Intel интегрировала ускорение FEC непосредственно в процессоры Xeon EE в рамках технологии vRAN Boost. Эксперименты с FPGA от AMD выявили их недостаточную энергоэффективность, а применение GPU NVIDIA оказалось экономически нецелесообразным для данной функции.

Однако развитие концепции AI-RAN изменило экономические расчёты, поскольку теперь одни и те же ускорители можно задействовать как для задач радиодоступа (RAN), так и для искусственного интеллекта. Это, в частности, вызвало интерес Ericsson к тензорным процессорам (TPU) от Google. Тем не менее, несмотря на декларируемую цель «единого ПО», практические шаги компании подтверждают сложности её реализации. Если уровни L2 и выше могут использовать общую кодовую базу для разного оборудования, то уровень L1 требует индивидуальной адаптации под каждый тип чипа.

Стремясь избежать привязки к одному поставщику микросхем, компания делает основной акцент на разработке слоёв аппаратной абстракции (HAL). Это позволит переносить программное обеспечение на различные аппаратные платформы с минимальными доработками. Ключевые усилия сосредоточены на внедрении интерфейса BBDev (Baseband Device) для отделения ПО радиодоступа от базового «железа». Также рассматривается возможность интеграции с платформой NVIDIA CUDA, но её реализация во многом зависит от прогресса в области отраслевой стандартизации.

В области радиосвязи, которую сложнее всего перевести в полностью виртуальную форму, Ericsson интегрирует процессоры Neural Network Accelerators (NNA) прямо в радиооборудование. Эти программируемые матричные ядра специально созданы для эффективной обработки информации в системах Massive MIMO, выполняя формирование луча и анализ канала за миллисекунды при минимальном энергопотреблении. Модернизированные радиоинтерфейсы с поддержкой ИИ включают в себя специализированные чипы Ericsson с NNA. По заявлениям компании, это позволяет реализовать возможности локального принятия решений в системах Massive MIMO, что даёт возможность мгновенной адаптации в реальном времени.

Источник: