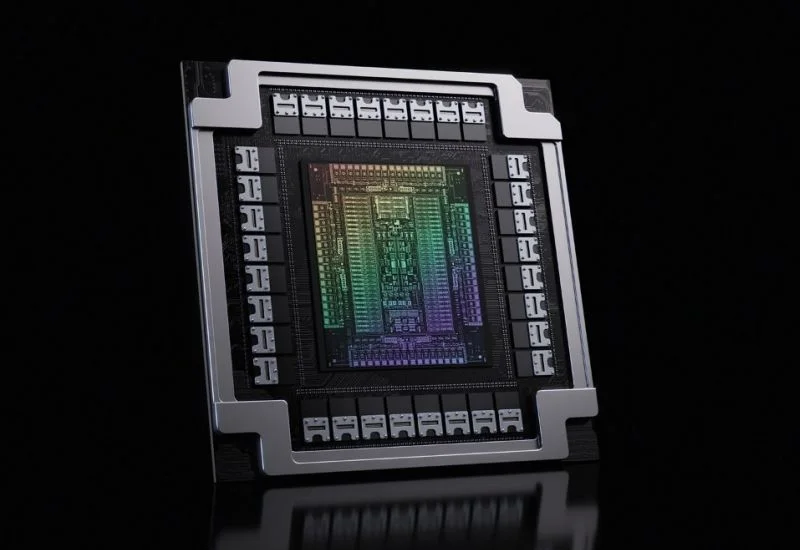

Согласно мнению экспертов, современные ИИ-ускорители подошли к такому рубежу, когда скорость обмена данными с памятью превращается в основное препятствие для дальнейшего повышения производительности. Вопросы ёмкости или нехватки самой памяти отходят на второй план, и преодоление этого ограничения ложится в первую очередь на плечи создателей графических процессоров и крупных языковых моделей.

Источник изображения: Nvidia

Как отмечает сооснователь Majestic Labs Ша Рабии (Sha Rabii) в материале CNBC, в то время как вычислительные ускорители в последние годы совершили огромный скачок в скорости, сопутствующая им память не демонстрировала столь же стремительного прогресса. Фактически, именно её пропускная способность сегодня сдерживает рост производительности больших языковых моделей. При этом переход к этапу инференса потребует ещё большего объёма памяти, что приведёт к резкому увеличению спроса. В целом, чем больше памяти в ИИ-инфраструктуре, тем больше запросов она может обработать одновременно. О необходимости наращивать производство памяти на выставке CES 2026 говорил и основатель Nvidia Дженсен Хуанг (Jensen Huang). Он даже упомянул, что покупатели игровых продуктов компании, таких как видеокарты и консоли, «недовольны» бумом ИИ, поскольку дефицит памяти толкает цены вверх даже в этих смежных рыночных нишах.

Даже запланированный AMD и Nvidia переход на память стандарта HBM4 не сможет полностью устранить проблему пропускной способности. Данный тип памяти по-прежнему ограничен числом доступных каналов и высотой стека кристаллов, не говоря уже о ширине шины. Масштабирование производительности вычислительных систем могло бы быть гораздо эффективнее, если бы не присущие HBM ограничения. Наращивание количества вычислительных ядер в GPU в такой ситуации теряет смысл, поскольку память не будет успевать поставлять данные для задач, связанных как с обучением больших языковых моделей, так и с их практическим применением.

Доступные производителям компонентов технологии сборки чипов также выступают в роли сдерживающего фактора: в условиях высокого спроса профильные производственные мощности перегружены, что усугубляет дефицит высокоскоростной памяти и увеличивает издержки компаний.

На уровне архитектуры инженеры исследуют такие подходы, как выполнение вычислений непосредственно в чипах памяти (PIM), повышение плотности размещения кристаллов в составе модулей памяти, а также внедрение в многокристальных сборках передовых интерфейсов, например UCIe, способствующих не только росту пропускной способности, но и сокращению задержек при обработке данных. Скорость будущего развития ИИ-инфраструктуры будет определяться успехами в области внедрения более быстрой памяти.

HBM4 обеспечит прирост производительности примерно в 1,5 раза по сравнению с HBM3E, благодаря более широкой 2048-битной шине, способной передавать до 2 ТБ данных в секунду. Ожидается, что к 2027 году появится память HBM4E, которая может повысить скорость передачи данных ещё в полтора раза. Внедрение интерфейса CXL также призвано улучшить эффективность обмена данными между компонентами вычислительных систем. Для памяти переход на CXL позволит увеличить коэффициент использования на 50% и снизить энергопотребление на 20–30%. Развитие новых методов трёхмерной компоновки памяти также должно способствовать росту производительности и уменьшению энергозатрат.