Компания Intel Foundry представила информационный буклет, в котором детально раскрываются её новейшие подходы к проектированию и производству аппаратных решений для задач искусственного интеллекта и суперкомпьютерных расчётов. Кроме того, Intel продемонстрировала «испытательный образец чипа для ИИ», наглядно иллюстрирующий текущие достижения компании в области корпусной сборки.

Источник изображений: Intel

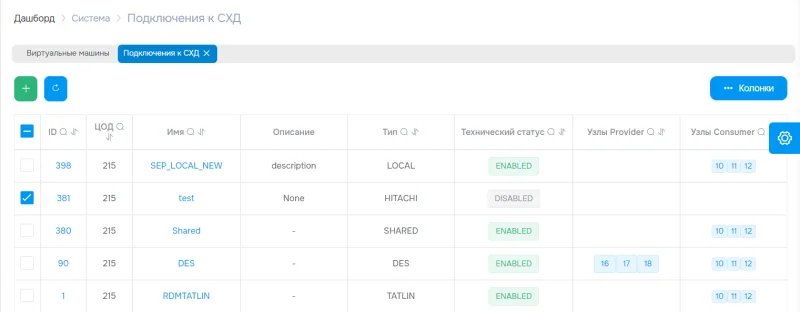

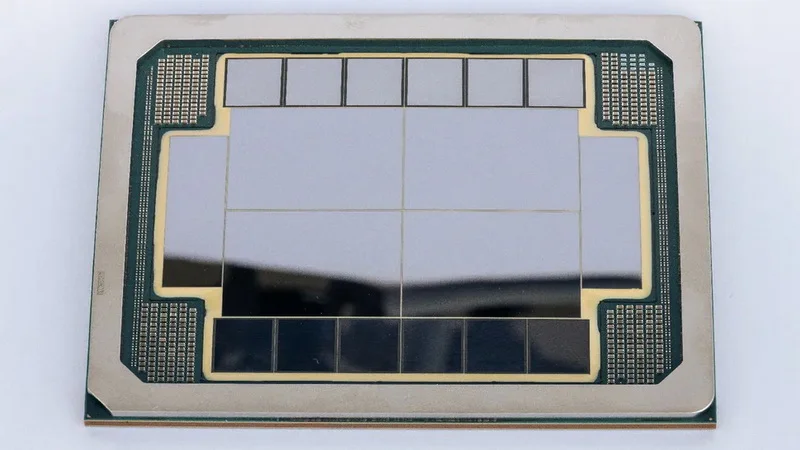

Была показана система в корпусе (SiP), занимающая площадь восьми стандартных фотошаблонов и содержащая четыре логических модуля, двенадцать блоков памяти уровня HBM4 и два интерфейсных блока. В отличие от более масштабной концепции с 16 логическими модулями и 24 стеками HBM5, представленной ранее, данная система уже готова к запуску в производство.

Ключевой момент: Intel Foundry продемонстрировала не готовый к работе ИИ-ускоритель, а именно «испытательный образец», который служит демонстрацией физической реализации (точнее, компоновки) будущих процессоров для ИИ и высокопроизводительных вычислений. Компания раскрывает целостную методологию проектирования, объединяющую крупные вычислительные блоки, модули высокоскоростной памяти, сверхбыстрые межкристальные соединения и современные системы питания в едином технологичном корпусе. Этот подход существенно отличается от решений, предлагаемых сегодня, например, компанией TSMC. Intel стремится показать, что процессоры нового поколения для высокопроизводительного ИИ могут быть построены по многочиплетной архитектуре, и Intel Foundry уже обладает возможностями для их изготовления.

Основу продемонстрированной платформы составляют четыре крупных логических блока, выполненных, предположительно, по техпроцессу Intel 18A (с использованием транзисторов RibbonFET и тыльной системы питания PowerVia). Они окружены стеками памяти класса HBM4 и интерфейсными модулями. Все ключевые компоненты соединены посредством 2.5D мостов EMIB-T, интегрированных непосредственно в подложку корпуса. Используемая технология межчиплетного интерфейса EMIB-T включает сквозные кремниевые переходы внутри мостов, что позволяет передавать питание и сигналы как по вертикали, так и по горизонтали, максимизируя плотность соединений и эффективность энергоснабжения. Платформа рассчитана на использование межкристальных интерфейсов UCIe со скоростью передачи от 32 ГТ/с и выше, которые, по всей видимости, также применяются для подключения стеков памяти C-HBM4E.

Испытательный образец процессора также отражает движение Intel в сторону вертикальной компоновки. В рамках своей технологической дорожной карты компания представила процесс Intel 18A-PT, созданный специально для чиплетов, предполагающих размещение дополнительных логических кристаллов или памяти поверх основного. Такая конструкция требует организации подачи питания с тыльной стороны, а также применения сквозных и комбинированных межсоединений. В представленном «испытательном образце ИИ-процессора» базовые кристаллы 18A-PT расположены под вычислительными кристаллами 18A/18A-P, выполняя роль либо крупного кэша, либо обеспечивая вспомогательные функции. Для вертикальной интеграции чиплетов Intel задействует семейство упаковочных технологий Foveros — включая Foveros 2.5D, Foveros-R и Foveros Direct 3D. Эти решения обеспечивают сверхплотные медные соединения между активными кристаллами, что позволяет достичь пиковой пропускной способности и высокой энергоэффективности для верхних слоев. В сочетании с мостами EMIB данные методы дают Intel возможность создавать гибридные горизонтально-вертикальные сборки, которые компания рассматривает как альтернативу крупным кремниевым интерпозерам, обеспечивая лучшее использование пластин и более высокий выход годных продуктов.

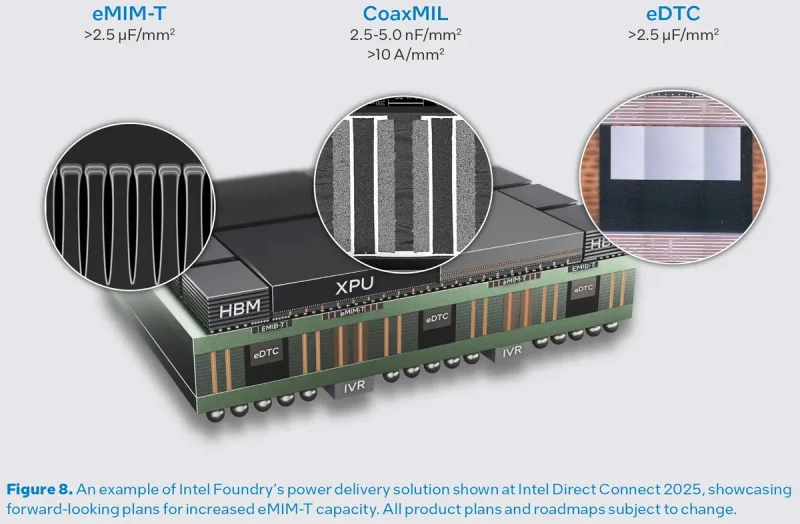

Ключевым конструктивным вызовом для многокристальных ускорителей ИИ и систем высокопроизводительных вычислений остается организация электропитания. Для этого платформа Intel должна интегрировать новейшие разработки компании в области энергоснабжения, такие как PowerVia, встроенные конденсаторы Omni MIM, развязку на уровне моста в EMIB-T, конденсаторы eDTC и eMIM-T на базовом кристалле, а также встроенные катушки CoaxMIL для поддержки полуинтегрированных регуляторов напряжения (IVR), размещаемых под каждым стеком и под корпусом (в отличие от решений TSMC CoWoS-L, где IVR являются частью интерпозера). Эта многослойная структура призвана обеспечивать стабильный ток в условиях рабочих нагрузок генеративного ИИ без просадок напряжения.

Данной демонстрацией Intel, по всей видимости, стремится заинтересовать потенциальных заказчиков. Пока остается неясным, будет ли архитектура, показанная сегодня, использоваться в новом поколении ИИ-ускорителей под кодовым названием Jaguar Shores, выпуск которых намечен на 2027 год.