Среди множества интересных анонсов, представленных CEO Nvidia Дженсеном Хуангом на осеннем мероприятии GTC 2025, особенно выделился центральный процессор с кодовым названием Vera — он содержит 88 физических ядер Olympus, созданных на архитектуре ARM и поддерживающих по два вычислительных потока на каждое. Примечательно, что энергопотребление данного ЦП заявлено всего около 50 Вт, что для x86-чипов с аналогичным количеством ядер выглядит крайне низким показателем. Ещё в 2014 году Nvidia уже начинала разработку центральных процессоров в рамках проекта Project Denver, результатом которого, к слову, стали серверные чипы Tegra. Однако именно ядра Olympus, по мнению многих экспертов, могут стать фундаментом для создания давно ожидаемых рынком ПК-процессоров под знаменитым чёрно-зелёным брендом. В любом случае, для серверных решений, особенно предназначенных для обучения и запуска генеративных моделей ИИ, архитектура ARM, относящаяся к семейству RISC, сегодня считается наиболее перспективной. Пусть ЦП на её основе пока уступают в производительности x86-аналогам (тем более что задачи ИИ обычно выполняются графическим процессором или тензорными ускорителями), зато они отличаются высокой энергоэффективностью и лишены ряда ограничений, свойственных CISC-платформе, где традиционно доминируют Intel и AMD.

Немного ранее, в сентябре, тот же Дженсен Хуанг наглядно продемонстрировал этот подход, отметив, что ИИ-серверы с графическими ускорителями Nvidia, соединёнными через NVLink, и процессорами x86 могут масштабироваться максимум до конфигурации NVL8 — то есть до восьми плат, управляемых одним ЦП. Это связано не с недостатками самих Intel Xeon, а с фундаментальными ограничениями шины PCIe, ключевого связующего элемента x86-платформы. В то же время на основе процессоров с ядрами ARM, включая перспективный Vera, можно создавать конфигурации вплоть до NVL72. Эта возможность, как уверен глава компании, открывает для ИИ-серверов на архитектуре ARM огромный рынок, глобальный объём которого оценивается примерно в 30 миллиардов долларов США. Однако возникает закономерный вопрос: если ARM — такая успешная процессорная архитектура, развивавшаяся десятилетиями, почему только сейчас заходит речь даже не о возможном вытеснении ею x86, а лишь о выходе её применения на сколько-нибудь заметный уровень в мировом масштабе?

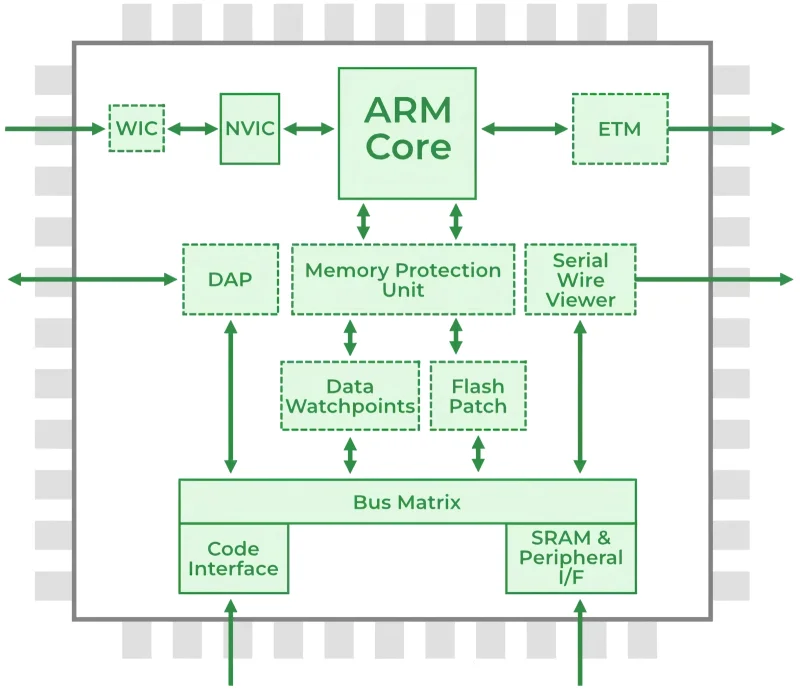

Структурная блок-схема процессора с архитектурой Advanced RISC Machine, известной как ARM (источник: GeeksForGreeks)

⇡#Целиком или по частям

Аппаратная организация процессора — то, как транзисторы объединяются в логические схемы, — тесно связана с набором команд, которые эти схемы выполняют: обе составляющие создаются в комплексе. На рубеже 1980-х и 1990-х годов, в период бурного роста ИТ-индустрии, конкурировали два основных подхода к проектированию процессорных архитектур и соответствующих систем команд (ISA): CISC и RISC. По сути, под «архитектурой процессора» обычно подразумевают именно его ISA, поскольку конкретные схемотехнические решения на кристалле могут меняться от поколения к поколению сильнее, чем набор инструкций, поддерживаемый процессорами одного семейства.

Таким образом, в 80-е годы прошлого века, помимо архитектуры x86 от Intel, развивавшейся с 70-х (именно в 1985 году она была расширена до 32 бит с выходом процессора 80386) и основанной на принципе сложного набора команд (CISC), пользователи могли выбирать из целого ряда компьютеров, использующих процессоры с упрощённым набором команд (RISC). К ним относились Sun Sparc, IBM/Apple/Motorola PowerPC, различные версии MIPS и другие. Термин «полная» команда в данном контексте означает, что она способна объединять вычислительную операцию практически любой сложности в небольшое количество инструкций переменной длины, вплоть до одной, даже если для её выполнения потребуется несколько тактов процессора. Физическая возможность выполнять сложные вычисления за минимальное число шагов обеспечивается особой организацией логических блоков внутри процессора, которые настроены на выполнение целых последовательностей операций, а не одной элементарной инструкции за раз.

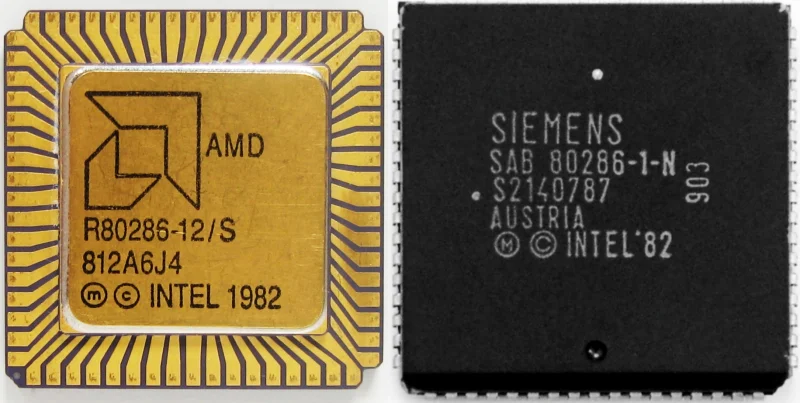

Ничего необычного; всего лишь CISC-процессоры Intel 80286, изготовленные в 1982 г. на предприятиях AMD (слева) и Siemens (источник: CPUMuseum)

В классическом курсе Computer Science Стэнфордского университета можно найти следующий наглядный пример: допустим, перед CISC- и RISC-процессорами поставлена одинаковая задача — умножить два числа из определённой таблицы (к слову, если матрицы будут разными, задача станет современной, превратившись в операцию матричного умножения, особенно востребованную сегодня в контексте генеративных нейронных сетей). У CISC-процессора для этого, разумеется, есть сложная инструкция (complex instruction) под условным названием MULT: компилятору достаточно записать её в виде

MULT 2:3, 5:2

Процессор самостоятельно, следуя правилам, определённым его системой команд (ISA) и реализованным во внутреннем микрокоде, обратится к оперативной памяти, где хранятся данные из ячеек исходной матрицы на позициях: второй столбец третьей строки и пятый столбец второй строки. Затем он сохранит эти значения в отдельных регистрах (расположенных вблизи его логических блоков), выполнит их умножение, поместит итог в другой регистр, а после отправит результат обратно в оперативную память, сделав его доступным для последующих операций. Компилятор для CISC-архитектуры, как видно, эффективно преобразует команды высокоуровневого языка в процессорный микрокод (ассемблер): сложные инструкции уже весьма близки к таким командам. Ещё одно важное преимущество этого подхода — экономичное использование оперативной памяти во время работы программы: для решения задачи требуется относительно немного инструкций, поскольку каждая из них выполняет заранее запрограммированную (на уровне ISA) последовательность действий.

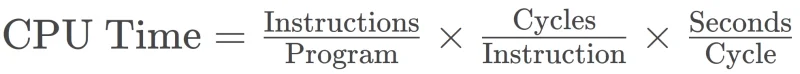

Время выполнения программы (величина, обратная ему, отражает производительность вычислительной системы), рассчитывается как произведение общего количества инструкций, среднего числа процессорных тактов на инструкцию и длительности одного такта. Подход CISC предполагает значительное сокращение третьего множителя за счёт роста второго, в то время как RISC действует противоположным образом (источник: Wikimedia Commons)

Как же справится с той же задачей процессор с сокращённым набором команд — RISC? Он выполнит те же действия, которые в CISC укладываются в инструкцию MULT, но пошагово: одна базовая команда, занимающая ровно один такт, за другой. Сначала такой процессор дважды обратится к оперативной памяти, чтобы загрузить нужные операнды в регистры (команда LOAD), затем перемножит полученные числа (PROD), после чего сохранит итог из регистра обратно в ОЗУ (STORE):

LOAD A, 2:3

LOAD B, 5:2

PROD A, B

STORE 2:3, A

Ассемблерный код для такой программы получается более объёмным и требует больше памяти. Его компиляция из исходного кода высокоуровневого языка также занимает больше времени и вычислительных ресурсов. Однако преимущества RISC-подхода столь же значимы: каждая упрощённая команда выполняется строго за один такт. Благодаря их элементарности, для аппаратной реализации на уровне полупроводниковой логики требуются гораздо более простые транзисторные схемы, что удешевляет производство и улучшает масштабируемость при уменьшении технологических норм. Конвейеризация (pipelining) в RISC-архитектурах также упрощается — опять же из-за фиксированного и одинакового времени выполнения каждой базовой инструкции. Ещё один аргумент в пользу сокращённого набора команд: после выполнения сложной инструкции CISC-процессор должен очистить используемые регистры, чтобы избежать смешивания данных между операциями. В RISC такой проблемы не возникает: даже если в части регистровой памяти остались данные с предыдущих тактов, следующая команда LOAD явно перезапишет их актуальной информацией. Это означает, что если один операнд используется многократно (как, например, при умножении матриц), нет необходимости тратить такты на его повторную загрузку из оперативной памяти — достаточно каждый раз обращаться к регистру, в котором он уже сохранён.

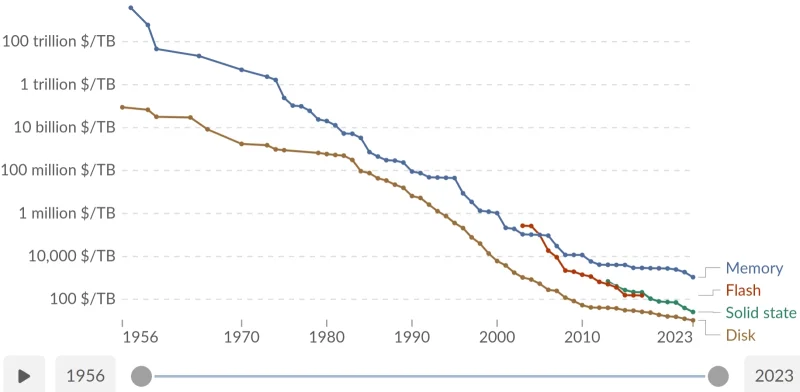

С середины 1950-х и до 2023 года стоимость одного терабайта компьютерной памяти снижалась почти линейно (в логарифмическом масштабе), однако с началом бума искусственного интеллекта ситуация усложнилась настолько, что исследование, завершённое в 2024 году, не смогло учесть самые актуальные на тот момент данные (источник: OurWorldInData)

⇡#За связь без брака

Если говорить точно, первые вычислительные машины почти поголовно использовали комплексные инструкции — в основном из-за крайне высокой стоимости любых типов памяти на рассвете компьютерной эпохи. Каждый байт, сохранённый на хранение команд в оперативной памяти, позволял обрабатывать немного больше данных одновременно, что в конечном счёте увеличивало общую эффективность системы — даже учитывая большее время, необходимое процессору для выполнения каждой сложной операции. Знаменитые компьютеры IBM System/360, PDP-11, VAX и многие другие по сути являлись CISC-платформами, однако само это понятие появилось лишь в конце 1970-х — когда началось проектирование архитектуры RISC, и все системы команд, не ориентированные на упрощение элементарных операций до уровня, исполняемого за один такт, стали причислять к категории CISC.

Любопытно, что сам подход RISC зародился из вполне конкретной практической потребности: в 1974 году в IBM создали прототип телефонного коммутатора (для медных аналоговых линий, естественно — откуда в то время взяться другим?), который мог устанавливать соединения между 300 парами абонентов в секунду — невообразимый для того периода показатель. Однако возникла проблема: компьютеры того времени — по крайней мере те, которые операторы связи могли массово размещать на своих узлах, — не обеспечивали достаточного быстродействия для управления столь скоростным контроллером. Это устройство, как признавали в самой компании, уже собирались отложить в сторону — в надежде, что со временем эволюция вычислительных систем естественным образом приведёт к появлению более быстрых машин. Но команда Джона Коука (John Cocke), работавшая над коммутатором, проявила упорство — и предложила идею кардинально повысить производительность систем (тех, что были доступны; на существующей элементной базе) именно за счёт применения ограниченного набора коротких команд, не требующих длительного времени выполнения. Очевидно, что круг задач телефонного коммутатора крайне ограничен — сложные инструкции для управляющего компьютера просто не были нужны. Великая заслуга Коука и его группы заключается в том, что они не сосредоточились на создании специализированного контроллера для единственного приложения, а сформулировали фундаментальный принцип, лёгший в основу RISC как программно-аппаратной архитектуры: «Не стоит усложнять вычислитель, если это усложнение не окупается» (don’t add complexity unless it pays for itself).

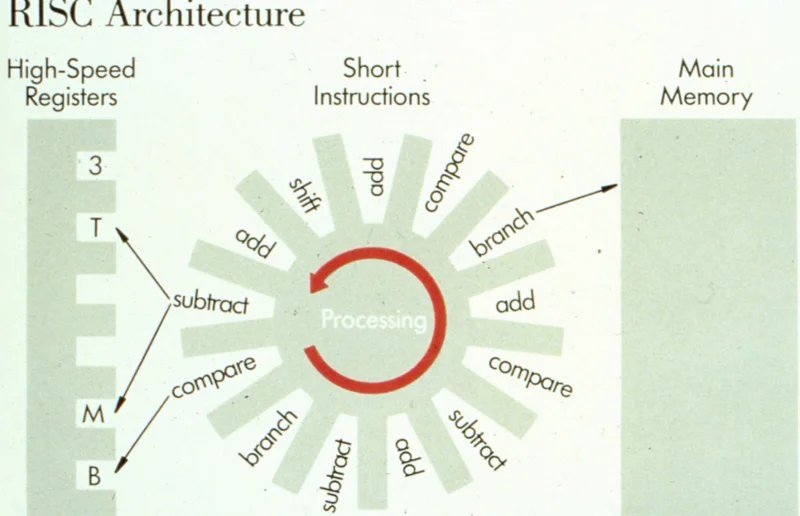

Иллюстрация из раннего доклада команды Коука, демонстрирующая ключевые идеи архитектуры RISC (источник: IBM)

В 1980 году команда под руководством Коука продемонстрировала первый прототип универсального RISC-компьютера (не ограниченного исключительно задачами телефонии), который получил название IBM 801 — по номеру здания, где располагалась лаборатория. За этим последовали другие системы, основанные на аналогичных принципах — выполнение каждой инструкции за один такт, конвейерная обработка, увеличенное число регистров для ускорения доступа к данным, — созданные сторонними разработчиками: Stanford MIPS, Berkeley RISC 1 и 2 и другие. К началу 1990-х различные реализации процессоров с сокращённым набором команд начали появляться одна за другой: среди них можно выделить Sun SPARC (Scalable Processor Architecture) и PowerPC — совместную разработку Apple, IBM и Motorola. Однако с расширением рынка персональных компьютеров архитектура CISC, на которую, вопреки тенденциям, сделала ставку Intel, не только стала преобладать, но и утвердила почти полное господство (сложную историю переходов Apple между CISC и RISC пока опустим). Объясняется это явление довольно просто: действием мощного эффекта положительной обратной связи в экономическом смысле.

Изначально архитектура центрального процессора строго задавала, какое программное обеспечение сможет работать на компьютере с таким ЦП: возможность виртуализации возникла гораздо позже, когда вычислительная мощность оборудования возросла в разы. Здесь огромную роль играет экономический фактор: чем более распространённой становится определённая программно-аппаратная экосистема, тем больше объёмы её продаж — и тем ниже себестоимость каждого отдельного компьютера. Первоначальные постоянные издержки — на разработку набора команд (ISA), проектирование под него процессора, аренду производственных мощностей для выпуска чипов (при отсутствии собственного завода) — для конкурирующих экосистем примерно одинаковы. Дальнейшее же зависит от масштабов сбыта: чем больше продано процессоров, тем больше знаменатель в формуле расчёта себестоимости одного ЦП (в числителе — те же постоянные затраты плюс переменная часть, фактическая стоимость изготовления одной микросхемы, которая ничтожно мала по сравнению с постоянными расходами). Разработчики программного обеспечения также стремятся продать как можно больше копий своих продуктов и потому предпочитают создавать их под самые популярные платформы. Таким образом, на открытом рынке — где изначально нет монополии какой-либо проприетарной, не лицензируемой сторонним производителям ISA — рост спроса на оборудование определённой архитектуры стимулирует продажи совместимого с ним ПО, и наоборот. Возникает положительная обратная связь, благодаря которой за относительно короткий срок одна из конкурирующих экосистем естественным образом захватывает доминирующее положение.

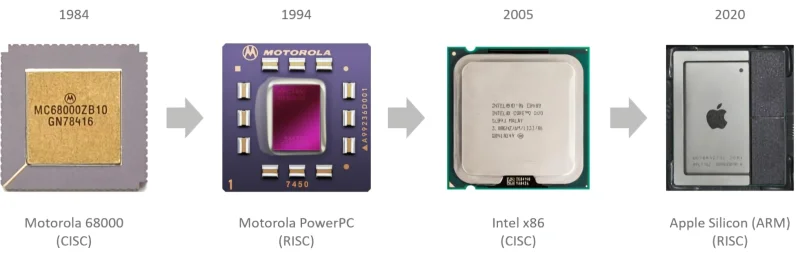

Переходы Apple Mac (ранее Macintosh) между двумя фундаментально разными ISA практически не сказывались на удобстве конечных пользователей этих компьютеров, поскольку программное обеспечение проприетарной экосистемы под знаком надкушенного яблока всегда оперативно и полностью переносилось на новую процессорную архитектуру (источник: Apple)

⇡#Выход на сцену Intel

Сегодня американская корпорация известна как разработчик самой распространённой в мире архитектуры центральных процессоров x86, однако изначально, с момента основания в 1968 году, она планировала заниматься созданием и производством компьютерной памяти — и на протяжении почти двадцати лет активно развивала именно это направление. Первый центральный процессор, 4-битную модель 4004, Intel выпустила в 1971 году, во многом случайно — выполняя заказ японской компании Busicom, производившей калькуляторы. Несмотря на то, что эта микросхема с шестнадцатью выводами поддерживала довольно ограниченный набор из всего 46 команд, технически она полностью соответствовала принципам архитектуры CISC, поскольку её инструкции представляли собой сложные операции, сочетающие обращение к памяти и вычислительные действия. Компания осталась верна выбранной архитектуре, представив спустя несколько лет 8-битные чипы 8008 и 8080. Последний, кстати, стал основой для одного из первых персональных компьютеров под именем Altair 8800, выпущенного в 1974 году американской фирмой Micro Instrumentation and Telemetry Systems (MITS). Эта модель примечательна в истории ИТ-индустрии тем, что именно для неё в компании Micro-Soft (до начала 1980-х название писалось через дефис), основанной Биллом Гейтсом (Bill Gates) и Полом Алленом (Paul Allen) в 1975 году, был создан интерпретатор Altair BASIC. Тем не менее, вплоть до середины 1980-х Intel по-прежнему считала производство оперативной памяти своим главным бизнесом, и лишь масштабное вторжение на этот рынок японских производителей DRAM (в результате которого доля Intel в мировых поставках сократилась за десятилетие, с 1974 по 1984 год, с 82,9% до 1,3%) заставило американского производителя микросхем всерьёз заняться развитием процессорного направления.

В 1985 году Intel по сути сделала рискованную ставку, выбрав путь разработки совершенно нового на тот момент 32-разрядного процессора 80386. При этом компания уже успешно поставляла свою 16-разрядную модель 80286, в том числе самой IBM для использования в компьютерах PC/AT (индекс 5170), представленных в 1984 году, а также множеству других производителей, осваивавших перспективную архитектуру IBM PC-совместимых систем. Как отмечал Пэт Гелсингер, в то время ведущий инженер Intel, а впоследствии её руководитель, переход к 32-разрядным ЦП для персональных компьютеров был смелым шагом в неизвестность: подобные процессоры тогда создавались в основном для мэйнфреймов и мини-компьютеров, таких как DEC VAX-11/780. Однако с коммерческой точки зрения этот риск оказался обоснованным, поскольку бесспорный лидер рынка ПК того времени, IBM, активно развивала собственную 16-разрядную операционную систему OS/2. Ещё немного — и зарождавшаяся открытая платформа, позволявшая любому производителю собирать компьютеры из стандартных компонентов и использовать независимо разработанные ОС, могла бы исчезнуть, что коренным образом изменило бы мировой компьютерный рынок. «IBM полностью контролировала архитектуру OS/2 — от приложений и операционной системы до аппаратной части, —